发布日期:2024-03-01 浏览量:1125

字号:大 中 小

所属领域

智能制造

痛点问题 随着光模块高速发展,AI和数据中心要求速率越来越高,体积越来越小,传统的PD打线键合已然满足不了市场需求,主要体现在: ①信号延迟与寄生电感 较长的键合丝不仅增加了信号传输的路径长度,还引入了不可忽视的寄生电感,这对于高速信号传输,无疑是一大痛点; ②散热性能 打线键合,芯片产生的热量需要通过芯片背面的散热路径传导至封装基板,效率相对来说很低,限制了芯片在高功率密度应用中的表现; ③引脚密度和面积限制 受限于键合丝的物理尺寸和芯片布局空间,引线键合的I/O引脚密度难以大幅度提升,难以满足日益增长的集成度需求。

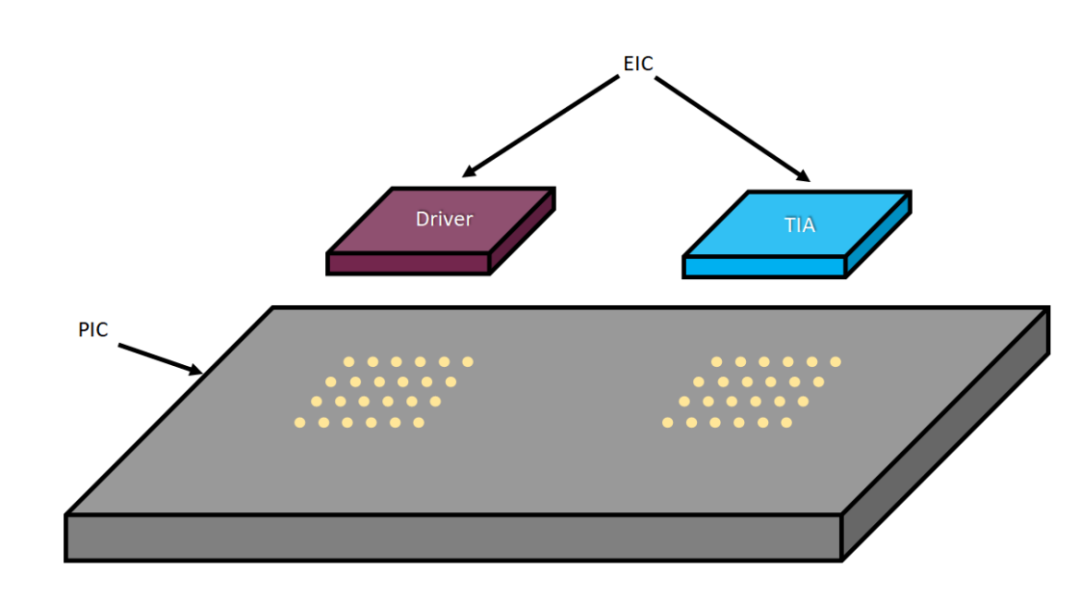

解决方案 倒装键合(Flip chip)大大可以改善封装技术的格局,芯片通过凸点直接与封装基板的焊盘进行电气互连接,芯片的正面朝下,实现了“翻转”式的连接。

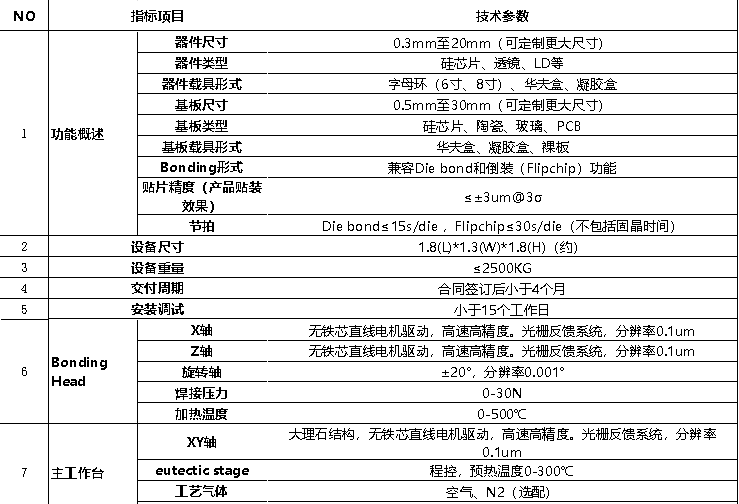

技术指标

相关技术指标如下表:

表1 技术指标

竞争优势 ①800G/1.6T…..高速模块信号路径优化 倒装键合技术省去了长的键合丝,信号可以直接通过凸点与基板连接,大大缩短了信号路径,有效减少了信号延迟和寄生电感,为后面的高速模块数据传输提供了可能 ②器件散热性能更好 芯片与封装基板的直接连接,使芯片热量更好的传递到基板上面,并通过散热系统散发出去,显著提高了散热性能,为高性能、高功耗模块运行提供了可能 ③可靠性更高 倒装技术允许在芯片表面布置更多、更密集的凸点,从而实现更高的I/O引脚密度,有效节省了封装面积,为小型化、集成化提供了技术支持,也为器件可靠性提供了保证

技术成熟度 已有样品/样机。

产业化应用 随着半导体的技术的不断发展,倒装芯片也在持续进化,向着更高集成度、更低功耗、更高速度的方向迈进。一方面,随着新材料、新工艺的应用,凸点尺寸不断缩小,I/O引脚密度不断提升,为芯片的小型化和集成化提供更多的可能;另一方面,倒装芯片技术与先进的封装技术(如2.5D/3D IC封装)的结合,正逐步打破传统封装的界限,推动着半导体封装技术向更高层次迈进。 同时,随着人工智能、物联网等新领域的兴起,对TCB键合精度、高可靠性、高稳定性提出更高的要求,TCB热压倒装键合技术作为提升器件的关键手段之一,将在这些领域发挥更加重要的作用。

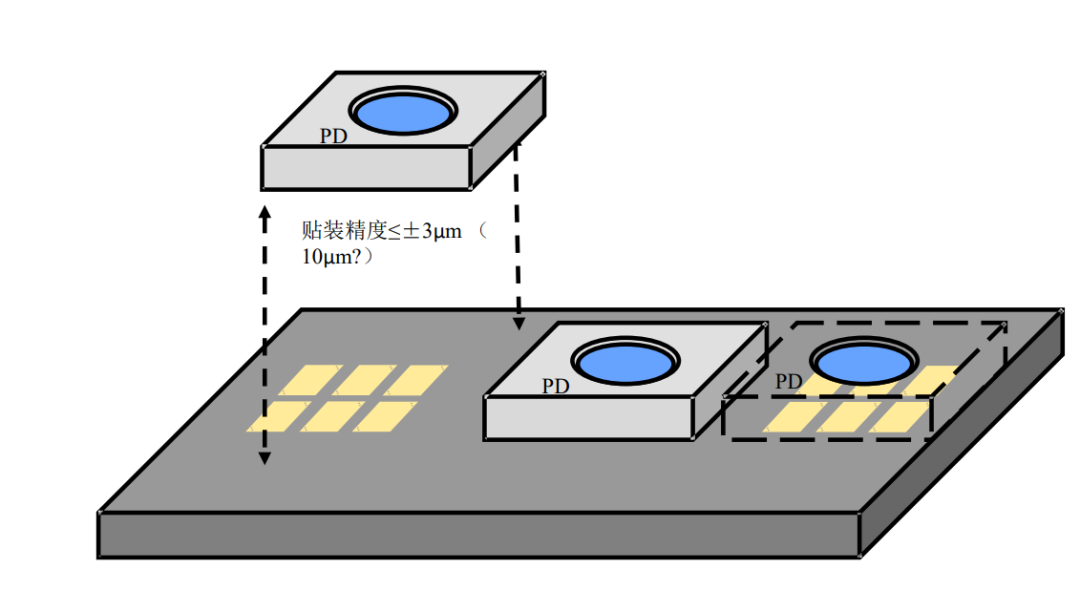

应用案例:

①倒装PD贴到TIA

②倒装PD贴到PCB基板

发展规划: 2024年:年底交付首台设备 2025年:获取光通讯大厂试样或订单 2026年:在国内外建立相对稳定化的市场规模

知识产权: 该成果已申请/授权多项中国发明专利。

合作方式:

专利许可、专利转让、作价入股、技术开发、面谈等。